基本信息

- 项目名称:

- 基于ARM+FPGA的视频数据采集装置

- 来源:

- 第十二届“挑战杯”省赛作品

- 小类:

- 机械与控制

- 大类:

- 科技发明制作A类

- 简介:

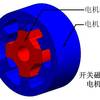

- 本作品设计了基于32位ARM7+FPGA的图像处理硬件平台和基于μCOS-II 实时操作系统的图像处理软件平台,以低廉的成本和良好的实时性实现了高速图像处理。 系统利用FPGA强大并行性、可重构特性以及其丰富的逻辑资源,做数据量大,计算复杂度简单的图像处理;利用ARM7其强大的计算能力来处理计算复杂度高、数据量小的图像处理。本装置成本低、体积小、实时性高、有可重构性,有着非常好的产业化前景。

- 详细介绍:

- 1原理:现代化生产和科学研究对图像采集系统的要求日益提高,传统的图像处理平台成本高、实时性低、处理功能简单,不能很好的满足用户多样化的应用要求。故本作品设计了基于32位的ARM7+FPGA的图像处理平台。 2创新点: (1)系统利用FPGA强大并行特性、可重构特性以及丰富的逻辑资源,做数据量大,计算复杂度简单的图像处理,比如格式转换和图像灰度化,中值滤波等。 (2)利用ARM7其强大的计算能力来处理计算复杂度高、数据量小的图像处理,比如边沿检测,轮廓提取等。 3关键技术:本作品设计了基于32位的ARM7+FPGA的图像处理硬件平台,和基于μCOS-II实时操作系统的图像处理软件平台,以低廉的成本和良好的实时性实现了高速图像处理。 4市场前景: 本装置成本低、体积小、实时性高、有可重构性,有着非常好的产业化前景。

作品专业信息

设计、发明的目的和基本思路、创新点、技术关键和主要技术指标

- 本作品以低成本的32 位的ARM7单片机+FPGA 架构,在μCOS-II 实时操作系统环境下设计了嵌入式的数据采集系统,创新点在于提出图像处理的“CMOS摄像头+FPGA+ARM”体系的可行性,并用硬件系统实现;使用FPGA作为系统的控制中心,实现图像的采集和处理,减少了硬件器件的使用,实现了系统小型化;充分利用FPGA内部丰富的逻辑资源,实现简单的预处理功能,减轻了ARM进行高级处理时的负担。

科学性、先进性

- 本系统对于图像底层处理,在高速图像采集系统中用FPGA 实现,采用HDL 编写图像处理算法,HDL 设计灵活、编程方便,易于在FPGA 中实现并行运算和流水线结构;对于图像高层处理,由ARM 单片机软件实现,基于ARM+FPGA 架构的图像数据采集系统,体积小,成本低,能满足一般工业控制场合的应用要求。

获奖情况及鉴定结果

- 无

作品所处阶段

- 实验室阶段

技术转让方式

- 可以

作品可展示的形式

- 实物、产品、图片

使用说明,技术特点和优势,适应范围,推广前景的技术性说明,市场分析,经济效益预测

- 1.具有标准VGA 视频数据输出接口,可以方便地连接标准的显示器,实现。采集的视频数据直接显示。 2.可以采用USB 接口的移动存储器存储采集的数据。 3.具有以太网接口,可以方便地连接互联网及局域网,实现视频数据的网络传输。 4.具有PS/2 接口,可以热拔插计算机标准键盘及鼠标。便于用户操作设置系统。 5.图像数据处理速度达到26fps@640×480。

同类课题研究水平概述

- 1.图像采集卡+PC 2. USB摄像头+PC 3. USB摄像头+ARM 4. CMOS+ARM 5. CMOS+FPGA+DSP 6. CMOS+FPGA+ARM 7. CCD+FPGA+ARM 方案1 PC机使用的要求比较高,并且处理效率一般,成本比较大。但实现容易,适合要求不高的一般领域。 方案2、3使用USB接口,能够方便设备的安装,但是由于USB摄像头采集的分辨率低,质量差,比较适合于安装调试方便,但对质量要求不高的领域。 方案4 用ARM直接接收来自摄像头的数据,同时进行处理,对ARM来说是一种负担,不推荐使用。 方案5、6 则用于高速度,并且对体积和功耗都有较高要求的图像采集和处理系统中,采集系统几乎全部的逻辑运算和控制都可以交给FPGA来完成,并且可以同时完成图像处理部分的底层算法;DSP则在数字信号处理方面有优秀的表现;ARM作为一款32位处理器,能够进行高级阶段的各种算法与控制,能够满足用户的要求。 方案7 CCD采集得来的图像数据的分辨最高,且速度最快,但是本系统对图像的要求暂时不需要求达到很高的标准,所以暂不考虑。